WoW 3DIC 技術

WoW 3DIC Technology

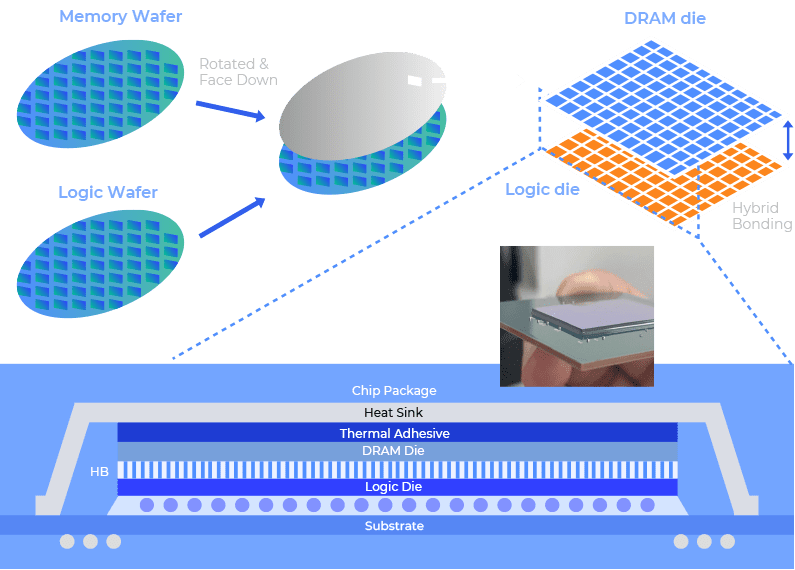

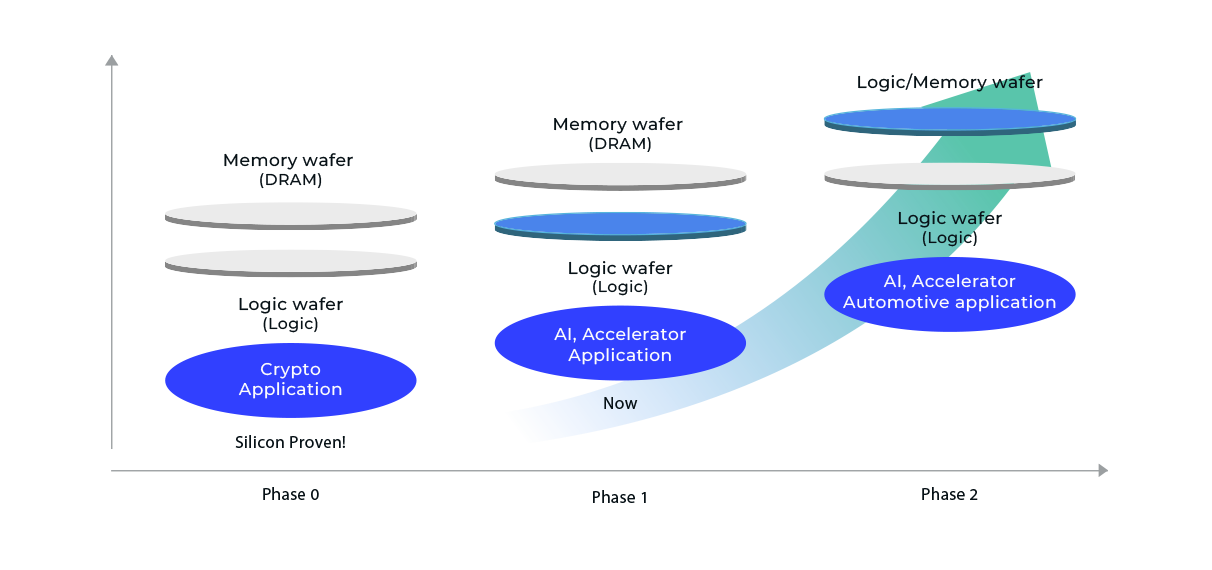

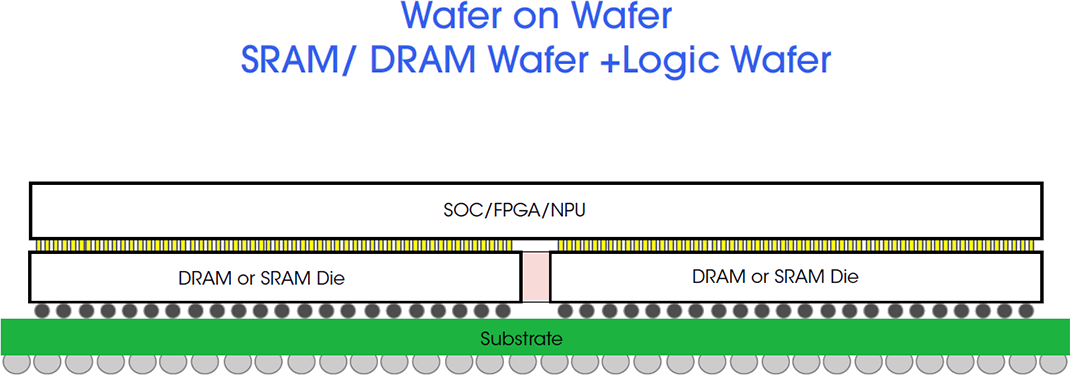

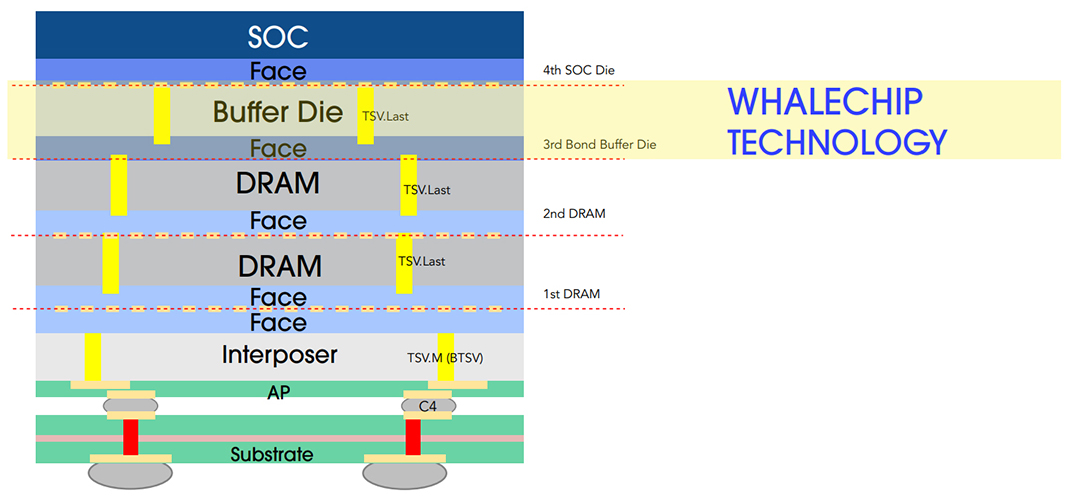

鯨鏈科技Wafer-on-Wafer (WoW) 3DIC技術採用先進的Hybrid Bonding晶圓級製造技術,將不同類型、不同結構甚至不同製程節點的晶片集成為一體。

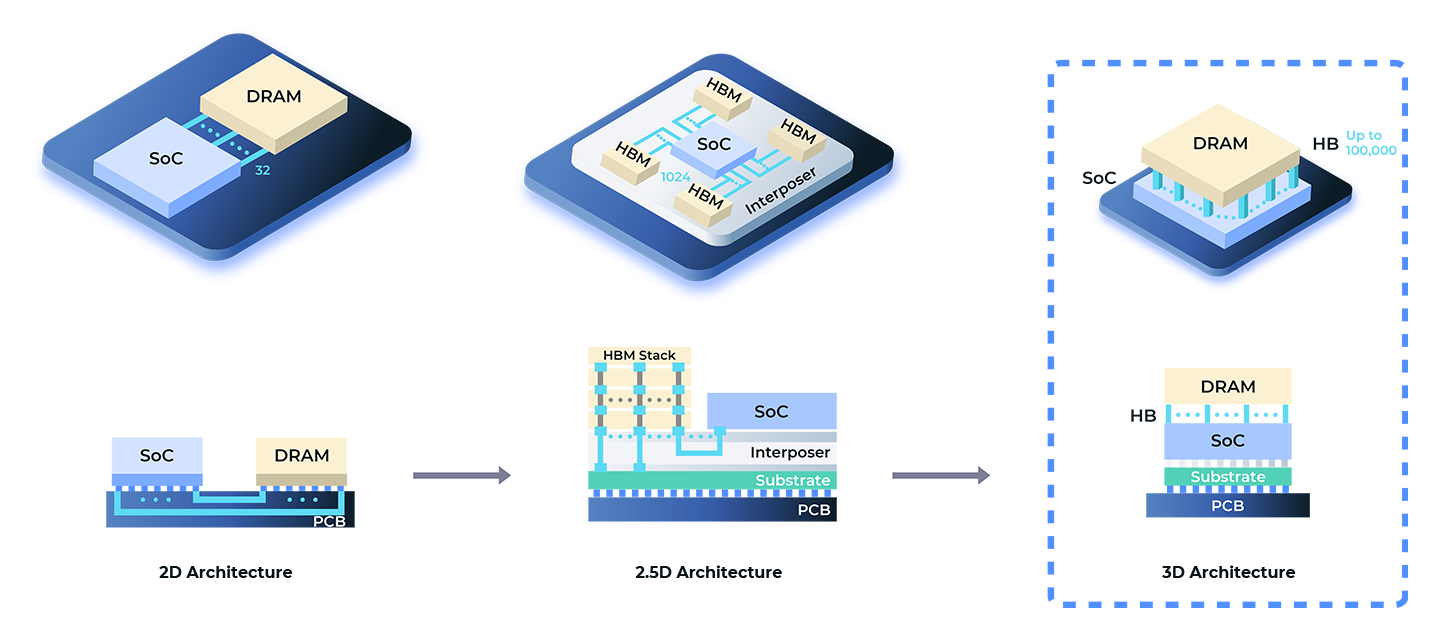

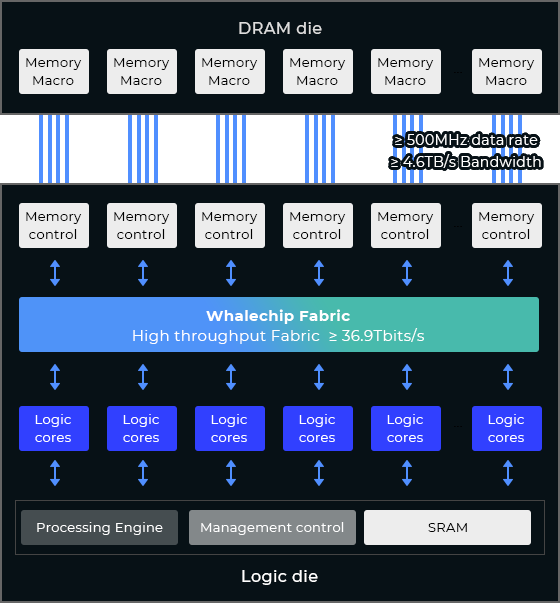

相較於2.5D CoWoS技術中SOC外接DDR/HBM方式,WoW 3DIC技術顯著提升了連線密度和數量,同時省去了PHY接口並大大縮短了連線長度。這些優化使得系統功耗和佔用面積顯著降低,資料傳輸頻寬大幅提升,解決了記憶體瓶頸問題,極大增強了晶片系統的整體計算性能

相較於2.5D CoWoS技術中SOC外接DDR/HBM方式,WoW 3DIC技術顯著提升了連線密度和數量,同時省去了PHY接口並大大縮短了連線長度。這些優化使得系統功耗和佔用面積顯著降低,資料傳輸頻寬大幅提升,解決了記憶體瓶頸問題,極大增強了晶片系統的整體計算性能