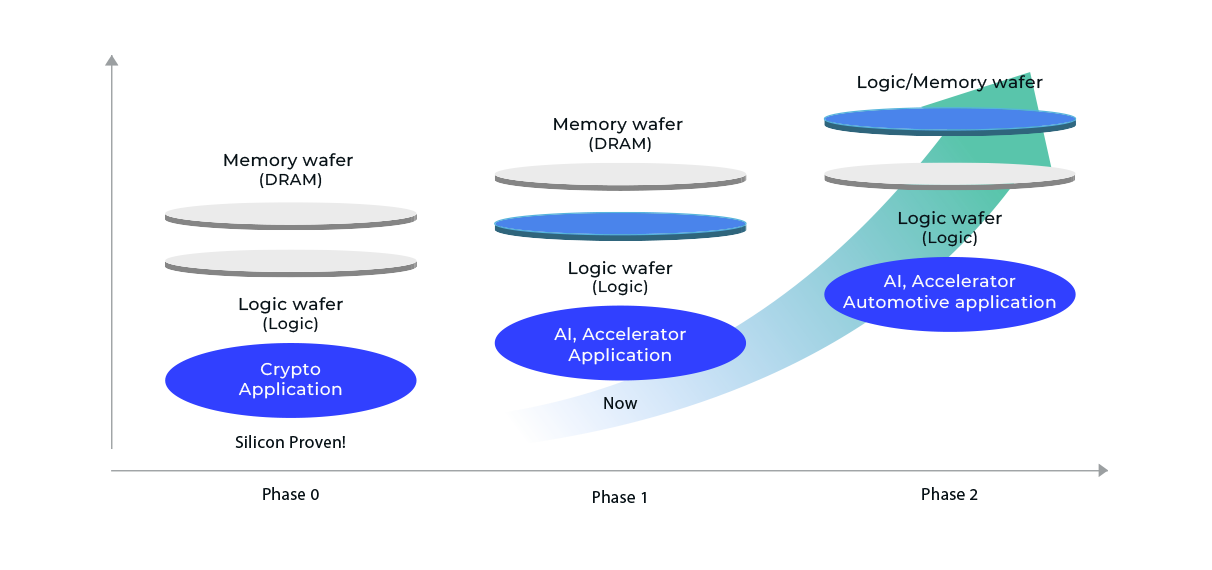

Next-Gen technology

3D Stacked Wafer-Scale Integration Solution

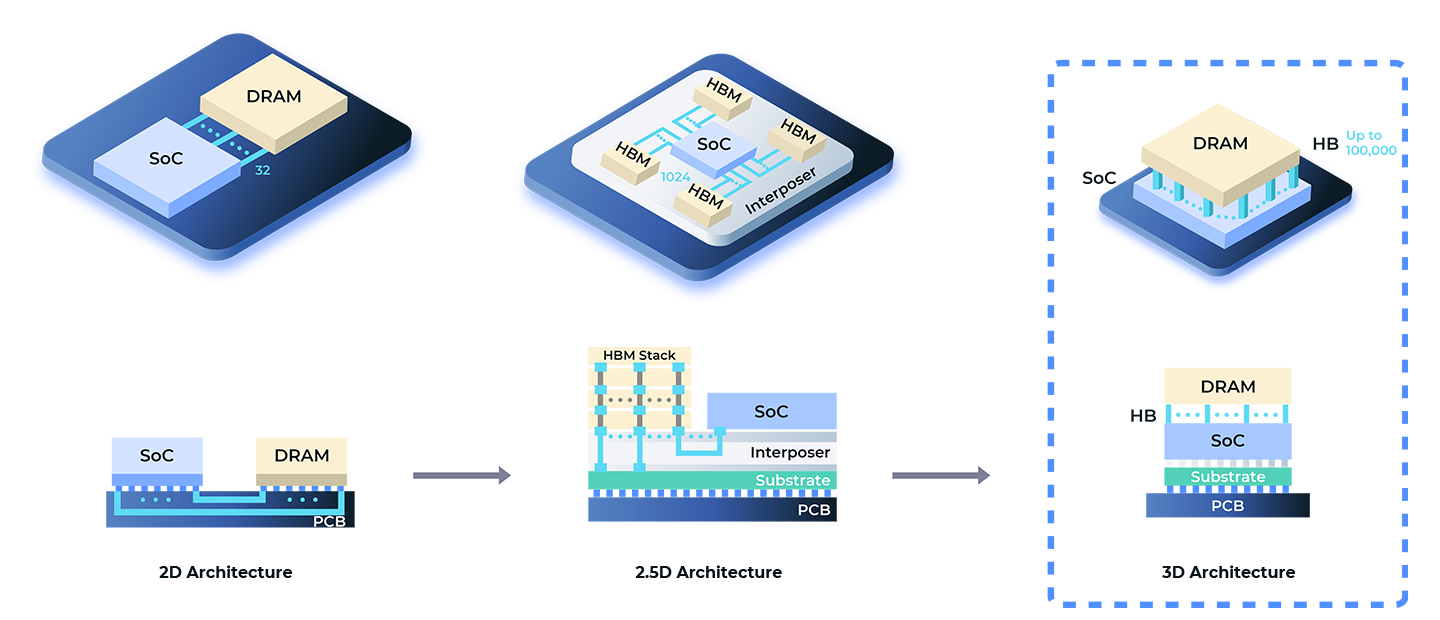

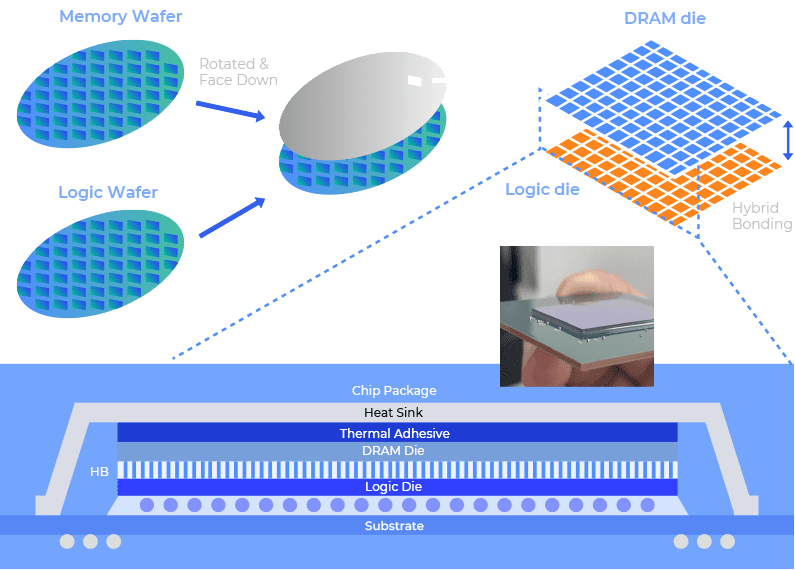

To achieve higher overall computing performance and memory bandwidth, we developed a wafer-scale stacked heterogeneous integrated 3DIC. This cutting-edge technology enables ultra-high interconnect density, reduced latency, and scalable performance for future chip designs.

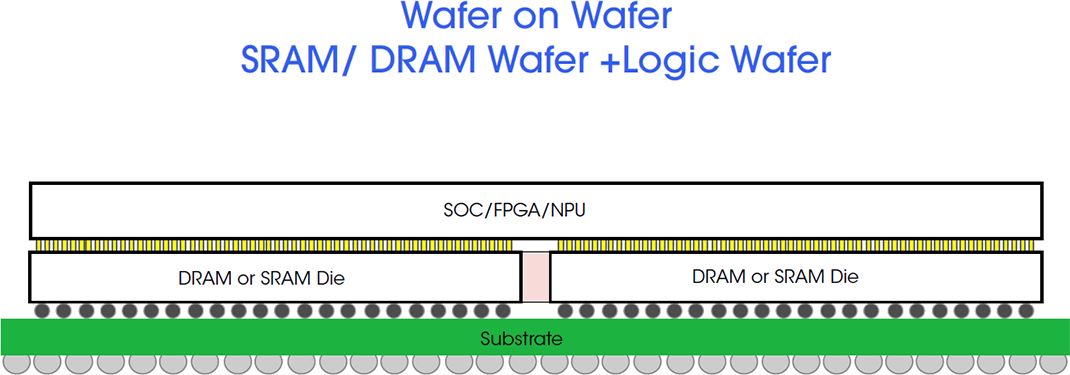

Advanced 3DIC Architecture for Next-Gen Computing

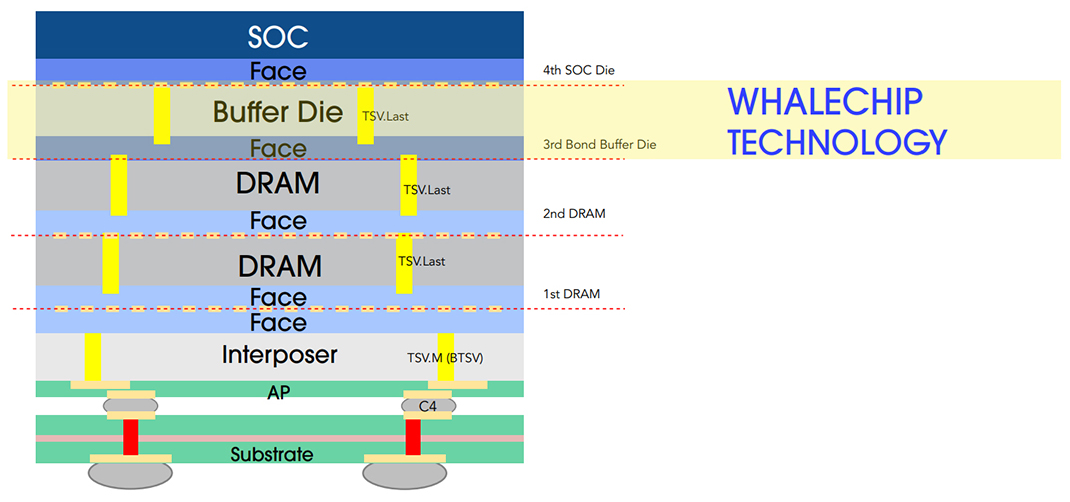

In WHALECHIP’s WoW 3DIC 2.0 architecture, stacking the SoC on top of 3D TSV DRAM helps reduce the SoC die area and minimizes the area overhead caused by TSV integration, enabling a more cost-efficient design for edge AI devices. Additionally, the top-layer SoC placement also contributes to improved system thermal performance

WHALECHIP Buffer Die Solution :

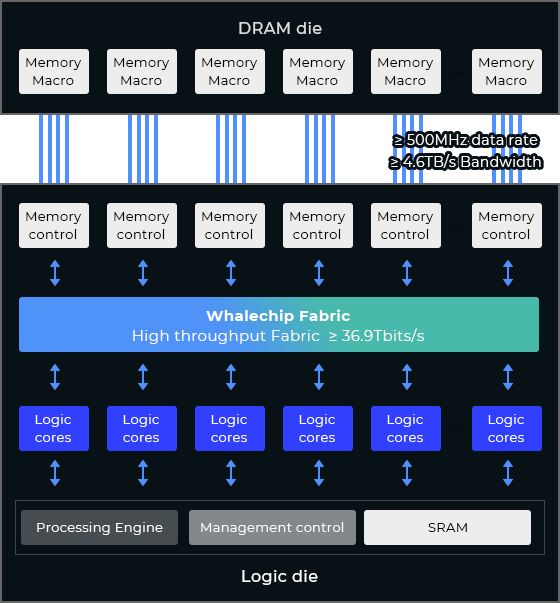

The WHALECHIP Buffer Die serves as a centralized control core with integrated memory controller functionality. It incorporates a DRAM controller, refresh controller, test and repair modules—such as MBIST, Repair, and ECC—as well as AXI and APB interfaces, providing comprehensive memory access control.

This architecture not only offloads memory management tasks from the SoC but also enables high-speed, low-power data exchange through close-proximity vertical stacking (with the SoC on top and Buffer Die in the middle), delivering a more efficient and optimized memory subsystem for high-performance computing (HPC) and edge AI applications.